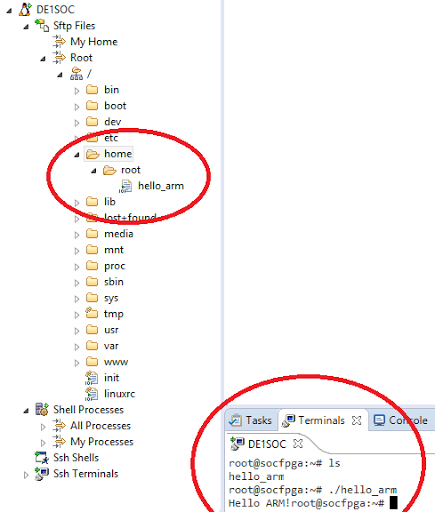

Dopo aver introdotto nel precedente articolo gli elementi principali del sistema, approfondiamo l’architettura del sensore CMOS OV8865.

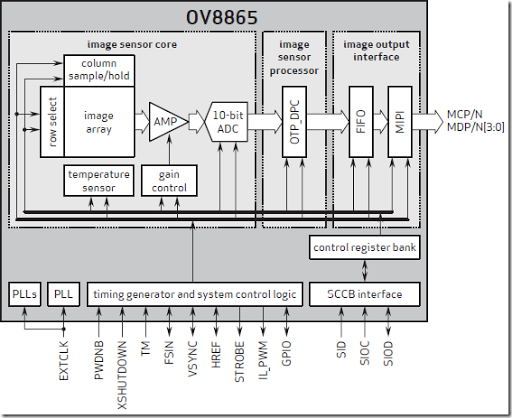

Il blocco principale è l’ image sensor core che si occupa di generare un flusso di dati digitali rappresentanti l’immagine, è composto da varie parti come illustrato nello schema sopra presentato tratto dal Product Brief di Omnivision.

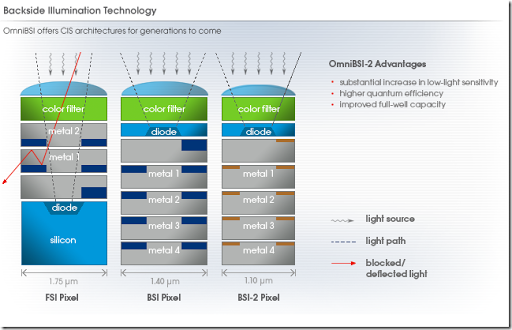

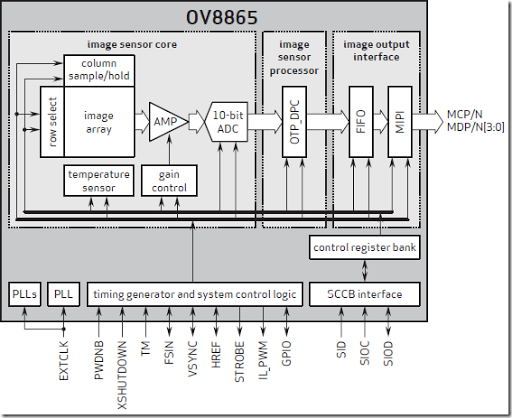

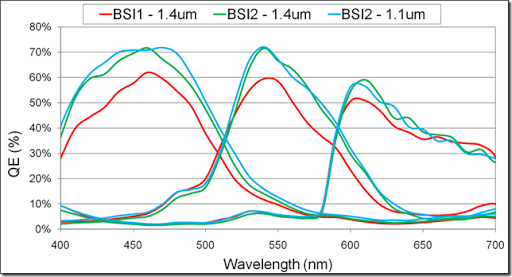

L’image array è composto da pixel con tecnologia BSI-2 (Back-Side Illumination), dove il fotodiodo è posto prima di altri strati. Una tale struttura permettte sostanzialmente una sensibilità maggiore. Termini come Quantum Efficiency e Full-Well Capacity che è possibile leggere nell’immagine seguente saranno maggiormente chiari tra poco.

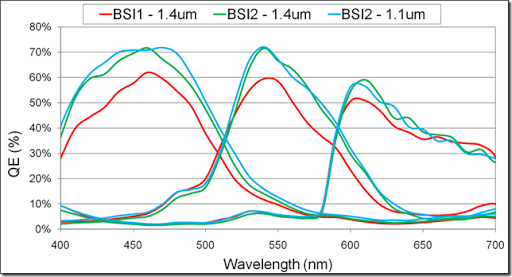

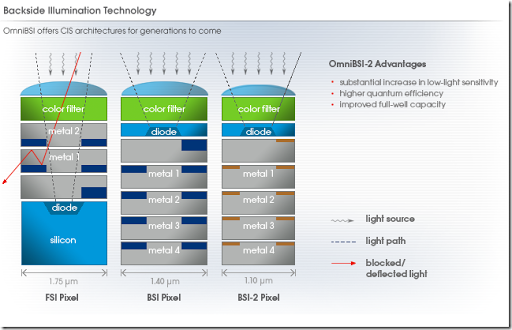

Senza approfondire troppo l’architettura elettronica dei pixel possiamo dire che il primo passo nel digitalizzare la luce è convertire i fotoni in elettroni, l’efficienza di questo processo è misurata dalla Quantum Efficiency (efficienza quantica). Ad esempio una Quantum Efficiency del 50% indica la generazione di 5 elettroni ogni 10 fotoni sul sensore. L’efficienza come mostrato dal grafico tratto dal paper The Mass Production of Second Generation 65 nm BSI CMOS Image Sensors di Omnivision varia in base alla lunghezza d’onda. Nel grafico sono mostrate per ogni tecnologia tre curve per le prestazioni dei canali R,G,B.

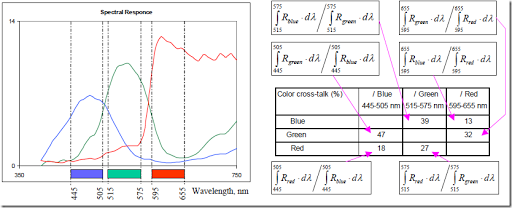

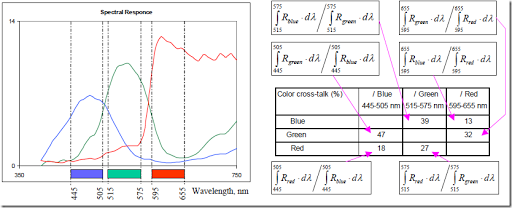

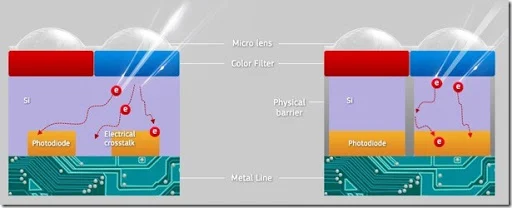

Con la tecnologia BSI-2 migliora inoltre il crosstalk ottico spaziale. In sostanza i filtri del colore (o Color Filter Array, CFA) sono posizionati ad una distanza non nulla dalla superficie dei fotodiodi a causa del metallo e/o degli strati isolanti. La luce proveniente ad un angolo diverso da quello ortogonale può essere assorbita dai fotodiodi adiacenti. Con la Back-Side Illumination, avendo il fotodiodo sopra agli strati di metallo si riduce questa distanza.

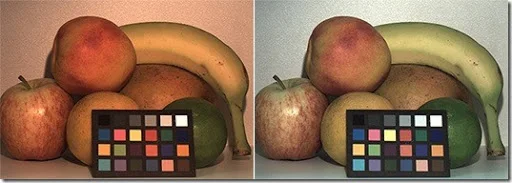

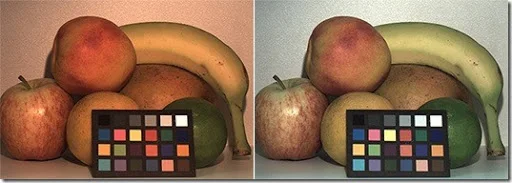

Tecniche di correzione del colore come ad esempio attraverso delle Color Correction Matrix (CCM) mirano a correggere tramite post-elaborazione il problema del crosstalk, che può avere anche origini di altra natura (es. crosstalk elettrico). Alcuni sensori integrano direttamente questa funzionalità, ottenibile altrimenti generalmente tramite ISP (Image Signal Processor) esterno.

A sinistra Color Correction Matrix disabilitata, a Destra abilitata. Fonte https://www.ptgrey.com/truecolor

A sinistra Color Correction Matrix disabilitata, a Destra abilitata. Fonte https://www.ptgrey.com/truecolor

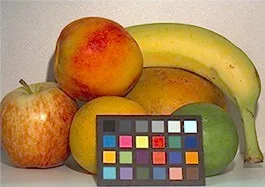

Sopra Color Correction Matrix applicata tramite l’app Color Corrector con illuminazione e gamma corrette in contemporanea

Dal grafico dell’efficienza quantica visto sopra è possibile notare il crosstalk delle varie tecnologie, di seguito sono riportate alcune formule di esempio per calcolare il valore numerico percentuale tratte dal paper Crosstalk and Sub-Pixel Distribution of Sensitivity in Color CMOS Image Sensor di Photobit, comperata da Micron, acquisita poi da ON Semiconductor.

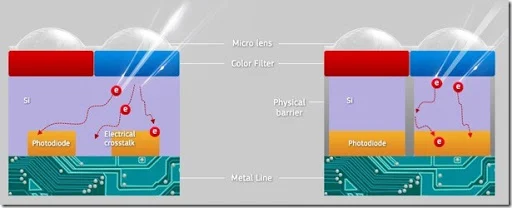

Tecnologie più recenti come PureCel di Omnivision o IsoCell di Samsung creano ulteriori barriere per minimizzare ulteriormente il crosstalk. E’ sotto illustrato il funzionamento di massima di IsoCell.

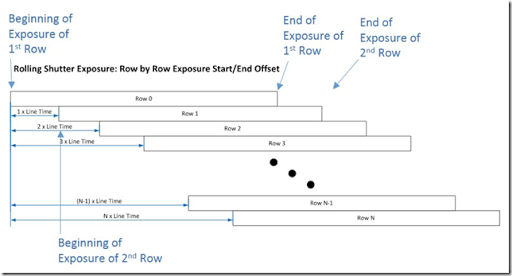

Prima della lettura i pixel vengono precaricati (pre-charging) nel cosiddetto Well (“pozzo” in italiano) la cui capacità è definita come Full-Well Capacity e dopo un certo periodo di tempo vengono campionati (sampling). Tra queste due operazioni la carica elettrica nei pixel decresce con l’esposizione alla luce incidente, questo intervallo di tempo è il cosidetto tempo di esposizione.Tanto minore sarà la carica elettrica letta sul pixel, tanto più luminoso sarà il suo valore. Tempi maggiori di esposizione permetteranno quindi di ottenere immagini più luminose.

NB: Il tempo di esposizione è un valore configurabile nel sensore OV8865 in unità di linee.

Curiosità: Il Range Dinamico (Dynamic Range) del pixel, cioè l’abilità di catturare sia oggetti molto luminosi che molto scuri in una singola immagine è dato dal rapporto tra il massimo segnale ottico che può essere rilevato senza saturare il Well ed il segnale ottico minimo rilevabile, limitato dal rumore.

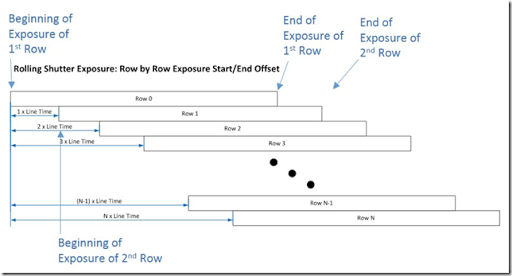

Da notare come le righe in questa tipologia di sensori vengano precaricate in sequenza, senza aspettare le letture complete delle righe precedenti, per ottenere frame-rate più elevati come mostrato nel seguente schema (tratto dalla tech note Rolling Shutter vs. Global Shutter di qimaging).

NB: Un ottimo testo per chi desiderasse approfondire l’elettronica e la fisica dei sensori CMOS è Image Sensors and Signal Processing for Digital Still Cameras redatto da Junichi Nakamura.

Dopo che il circuito di sample/hold ha campionato una riga di pixel, i dati vengono presentati uno alla volta nell’amplificatore analogico (indicato da AMP nello schema).

Il guadagno dell’amplificatore è personalizzabile ed è la strada per migliorare la luminosità dell’immagine dopo aver aumentato l’esposizione, è identificato anche come sensibilità ISO. Il segnale una volta amplificato viene digitalizzato dall’ADC a 10 bit.

UPDATE: E’ da ricordare che il segnale acquisito a 10 bit in questo caso non è sintomo di HDR. I valori acquisiti sono infatti lineari (chiaramente fuori dalle zone di saturazione) e per la visualizzazione “corretta” dovrà essere eseguita la correzione gamma (anche chiamata codifica gamma) in quanto i normali dispositivi si aspettano immagini di questo tipo. Durante questa procedura i valori saranno riportati in una scala più vicina alla percezione visiva umana secondo una legge di potenza e potrà essere prodotta un’immagine ad 8 bit senza troppi artefatti dovuti alla correzione.

Modificando, tramite appositi registri di controllo, la sequenza di campionamento è possibile capovolgere e/o rovesciare l’immagine (funzionalità di mirror e flip) evitando un post-processing e mantenendo così i consumi energetici molti contenuti. E’ anche possibile campionare solamente una sottofinestra dei pixel attivi (image windowing), funzionalità interessante nel caso in cui non tutta l’immagini serva per la propria applicazione ma solamente una ROI (Region Of Interest). Alcuni sensori, particolarmente orientati al controllo qualità tramite visione artificiale, permettono inoltre di definire più ROI.

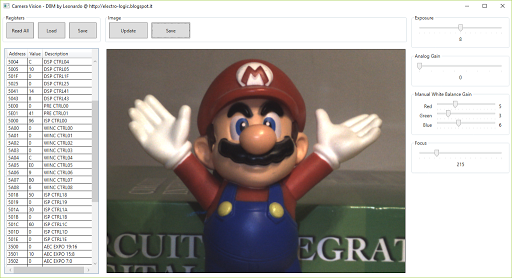

Il blocco successivo è l’ image sensor processor che include una piccola memoria OTP e funzionalità di Digital Signal Processor (DSP) come la Defective Pixel Cancellation (DPC), il Manual White Balance (MWB) e la Lens Correction (LENC).

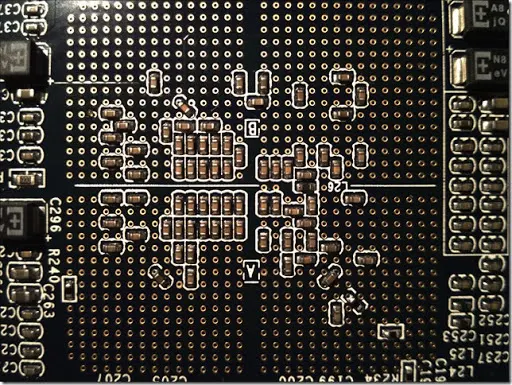

La cancellazione dei pixel difettosi permette di mascherare pixel morti (dead pixel) cioè sempre bianchi o neri, e generalmente anche i pixel feriti (wounded pixel) la cui luminosità non varia come gli altri pixel. Macchine fotografiche point-and-shoot presentano anche decine di pixel difettosi, considerato il numero totale di pixel però non è un problema così grave. Per chi fosse curioso ho caricato un archivio con una foto fatta con il modulo D8M con DPC attivato e DPC non attivato. Attenzione le foto sono PNG non compressi per non perdere le informazioni relative ai pixel difettosi e l’archivio pesa circa 9MB. I pixel difettosi di fabbrica, assieme ad altri elementi, possono inoltre creare una sorta di impronta digitale del sensore.

La memoria One Time Programmable (OTP) permette al produttore e al progettista di memorizzare una serie di informazioni come delle impostazioni di default alternative.

Il Bilanciamento Manuale del Bianco (MWB) permette di impostare un guadagno digitale distinto per i canali Rosso, Verde e Blu (R, G, B). Per una taratura manuale generalmente si inizia impostando al minimo tutti i guadagni, per poi aumentare gradualmente prima il Rosso ed il Blu. Il verde necessita infatti generalmente di un guadagno minore. Mantenendo i valori al minimo necessario si eviterà di amplificare ulteriore rumore.

I valori ideali del bilanciamento del bianco dipendono dall’illuminazione della scena inquadrata, una luce solare necessiterà di valori differenti da una luce al neon. Spesso vengono realizzati un insieme di combinazioni per le condizioni di illuminazione standard (es. soleggiato, nuvoloso, incandescente, fluorescente, etc..) ed il bilanciamento automatico (Auto White Balancing AWB), non fornito con questo sensore, provvede a scegliere la migliore nella più semplice delle ipotesi.

I modelli di macchine fotografiche più avanzate realizzano tecniche complesse per trovare il bilanciamento migliore, grandi passi in avanti sono stati compiuti rispetto ai primi modelli basati ad esempio su modelli di Gray World, dove si assumeva che l’immagine doveva contenere mediamente la stessa quantità di rosso, verde e blu. La tematica del bilanciamento automatico è ad ogni modo ancora oggi fonte di studio e miglioramento.

NB: Il guadagno digitale, se attivato, è applicato dal sensore OV8865 sui dati grezzi in uscita e sarà quindi presente anche salvando direttamente i pixel in uscita dal sensore prima di ulteriori elaborazioni (es. foto RAW).

UPDATE: A titolo di esempio sotto è illustrata una foto di un paesaggio con bilanciamento manuale impostato in modo non proprio soddisfacente, a destra il bilanciamento è disabilitato e la foto tende al verde essendo il colore più sensibile al sensore.

A sinistra foto con OV8865 con MWB attivato, a destra MWB disattivato

Alcuni dettagli come le sfumature delle nuvole e l’orologio del campanile sono però andati persi nel bilanciamento manuale. Eseguendo un bilanciamento automatico partendo dalla foto con MWB disabilitato è possibile correggere a piacere il bilanciamento, senza perdere ulteriori dettagli nella foto.

Foto precedente con MWB disattivato e corretta in post-processing col software RawTherapee: a sinistra col solo bilanciamento automatico del bianco, a destra con anche altre impostazioni modificate (Gamma non corretta in tutte le foto)

NB: Le foto a colori mostrate sono state demosaicizzate linearmente per brevità, presentano quindi difetti di vario tipo. Hanno inoltre una discreta quantità di micro-mosso visto che non è stato utilizzato un cavalletto.

La funzionalità di Lens Correction (LENC) serve per corregere la mancata uniformità di illuminazione dei bordi dell’immagine per difetti della lente, effetto chiamato anche vignettatura o lens shading. Sostanzialmente viene aumentato il guadagno dei pixel meno luminosi.

Foto con D8M (sensore OV8865) con LENC attivata a sinistra e disattivata a destra

NB: Questa funzionalità non corregge altri tipi di difetti introdotti da lenti non perfette, come le distorsioni radiali e tangenziali.E’ inoltre da ricordare che lo shading è dipendente dalla messa a fuoco del modulo e per un risultato ottimale bisognerebbe tenerne conto.

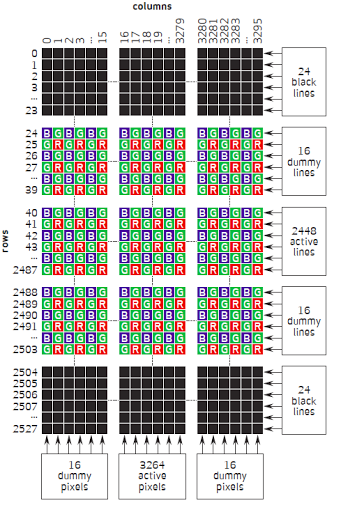

L’ultimo blocco del sensore è l’image output interface dove i pixel in uscita vengono bufferizzati in una memoria FIFO prima del loro invio serializzato tramite interfaccia MIPI.

Le specifiche MIPI CSI-2 sono disponibili solamente ai membri della MIPI Alliance previ abbonamenti che in data di stesura di questo articolo partono da 4000$ annui.

Il sensore permette di configurare il numero di lane (canali) da utilizzare per la trasmissione dei dati così come tutta una serie di parametri per ottimizzare la comunicazione (eventuali skew sui segnali, etc..).

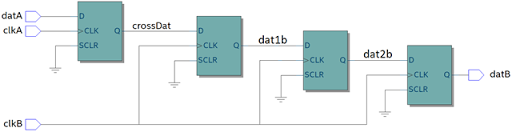

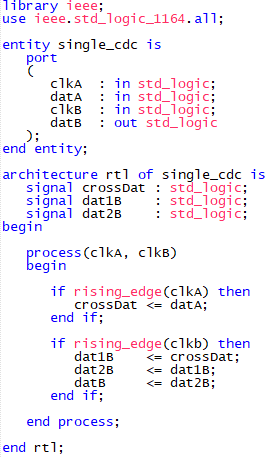

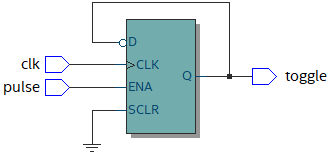

Il sensore dispone inoltre di un paio di PLL (Phase-Locked Loop) per generare i vari clock del sensore partendo da un singolo clock di riferimento (MCLK), nel nostro caso il clock di riferimento sarà generato dal convertitore MIPI TC358748XBG. I clock generati sono il clock dell’interfaccia MIPI, il Pixel Clock (o PCLK), il System Clock (SCLK) ed il DAC Clock. Particolare attenzione va riposta nella impostazione di queste frequenze, in quanto influenzano direttamente il frame-rate e la banda MIPI richiesta.

Il frame-rate è dato dalla formula:

FPS = SCLK / (HTS * VTS)

dove HTS è la Horizontal Total Size e VTS è la Vertical Total Size, ovvero il totale dei pixel orizzontali e verticali contando anche la regione di blanking. La regione di blanking (o dummy lines) è particolarmente importante e può essere impostata in modo tale da limitare il frame-rate per ovviare a problemi di banda MIPI. Il convertitore MIPI TC358748XBG ha infatti un buffer di linea interno limitato e picchi di banda prolungati potrebbero manifestare problemi in condizioni particolari.

Il tempo di esposizione è inoltre determinato sommando al valore del registro dell’esposizione il valore HTS mentre il valore VTS ne determina il valore massimo.

NB: Il Clock del DAC è probabilmente dovuto ad un ADC con architettura a pipeline o che comunque richieda un DAC.

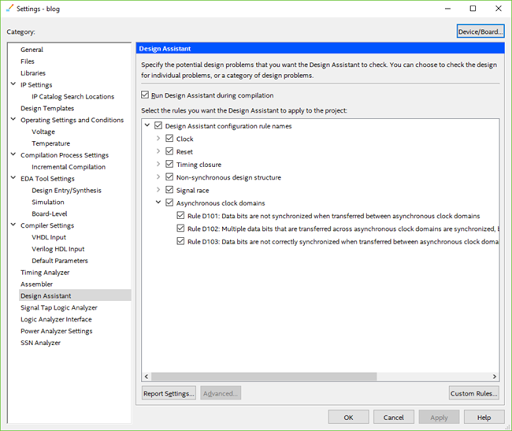

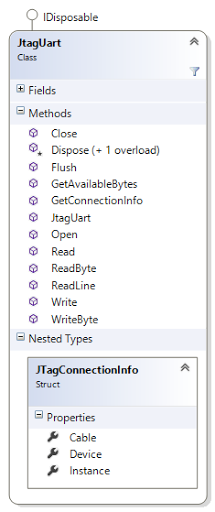

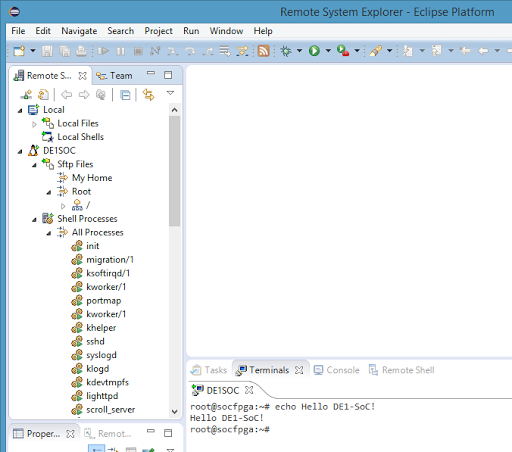

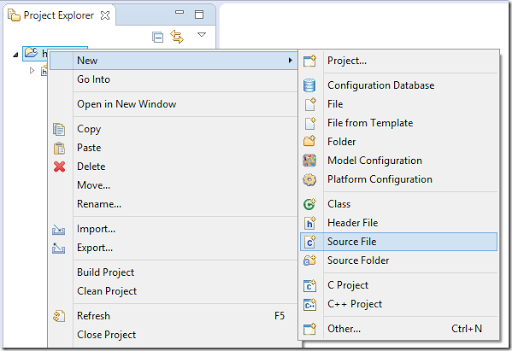

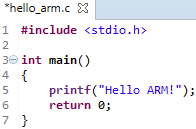

Dopo aver fatto una carellata delle funzioni disponibili, all’atto pratico possiamo configurare il sensore tramite l’interfaccia SCCB (Serial Camera Control Bus), un analogo del bus I2C. I registri di controllo purtroppo non sono in genere ben documentati ed il datasheet per quel poco che dice prevede una conoscenza teorica profonda del sensore, che spero di aver reso un poco tramite questo articolo.

Questa mancanza di documentazione probabilmente è in parte voluta sia per non diffondere troppi dettagli ai concorrenti sia in quanto un sensore d’immagine ben configurato può dare ad un dispositivo tecnologico un valore superiore tramite immagini visivamente accattivanti ed i produttori dei sensori sembra che vogliano in qualche modo lavorare direttamente insieme ai produttori dei dispositivi finali.